# MT6319 Product Brief

Version: 1.0

Release date: 2023-09-01

### The full datasheet is available with an NDA

Use of this document and any information contained therein is subject to the terms and conditions set forth in Exhibit 1. This document is subject to change without notice.

# **Version History**

| Version | Date       | Description      |

|---------|------------|------------------|

| 1.0     | 2023-09-01 | Official release |

# **Table of Contents**

|          |        | istory ·····                                                       |      |

|----------|--------|--------------------------------------------------------------------|------|

|          |        | Contents ······                                                    |      |

|          | _      | ures······                                                         |      |

| List     | of Tal | oles ······                                                        | 3    |

| 1        | Ove    | rview ·····                                                        | 4    |

|          | 1.1    | Features                                                           | 4    |

|          | 1.2    | Applications                                                       | 4    |

|          | 1.3    | General Description                                                | 4    |

|          | 1.4    | Ordering Information                                               | 5    |

|          | 1.5    | Part Voltage Table                                                 | 5    |

|          | 1.6    | Pin Assignment and Description                                     | 6    |

| 2        | Elec   | trical Characteristics ······                                      | 8    |

|          | 2.1    | Absolute Maximum Ratings over Operating Free-Air Temperature Range | 8    |

|          | 2.2    | Thermal Characteristics                                            | 8    |

|          | 2.3    | Pin Voltage Range                                                  | 9    |

|          | 2.4    | Recommended Operating Range ·····                                  | 9    |

|          | 2.5    | Electrical Characteristics ·····                                   | 10   |

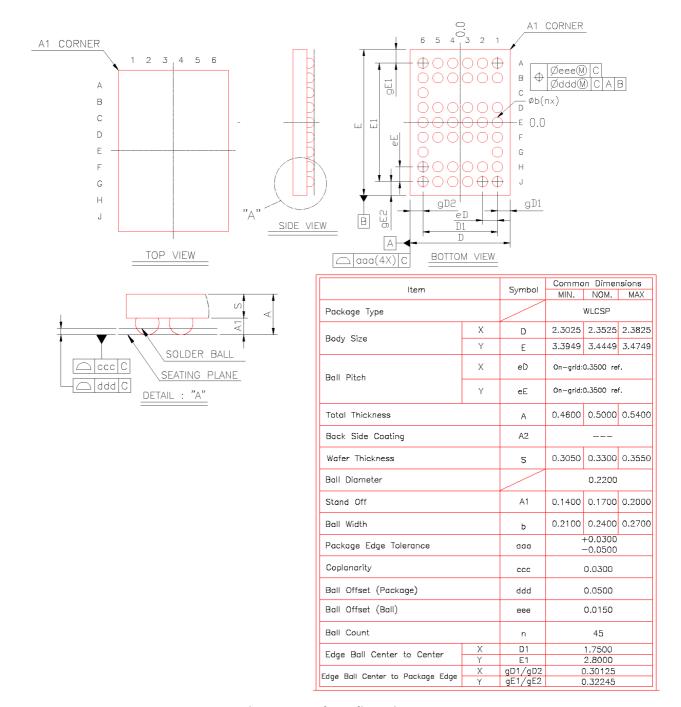

| 3        | MT     | 319 Packaging                                                      | 11   |

|          | 3.1    | Package Dimensions ·····                                           | 11   |

| Exhi     | bit 1  | Terms and Conditions······                                         | 12   |

|          |        |                                                                    |      |

|          |        |                                                                    |      |

|          |        |                                                                    |      |

| Lis      | t of   | Figures                                                            |      |

| Eigu     | ro 1 ' | L. MT6319 WLCSP 45L (2.35×3.44 mm) pin assignment ······           |      |

|          |        | L. Package dimensions ······                                       |      |

| rigu     | 16 5   | L. Fackage uniterisions                                            | . 11 |

|          |        |                                                                    |      |

| Lis      | tof    | Tables Tables                                                      |      |

| <b>-</b> |        |                                                                    | _    |

|          |        | Ordering option                                                    |      |

|          |        | MT6319 pin description                                             |      |

|          |        | Absolute maximum ratings ······                                    |      |

|          |        | Thermal Characteristics                                            |      |

|          |        | Pin voltage range ·····                                            |      |

|          |        | Operation condition ·····                                          |      |

|          |        | General electrical specifications ·······                          |      |

#### 1 **Overview**

#### 1.1 **Features**

- Four high-efficiency step-down DC/DC

- Max. output current 5A per phase

- Phases bundled up to a 4-phase converter

- Programmable over-current protection

- Programmable loop compensation for each phase configuration by eFuse

- Auto CCM/PFM, force-CCM operation and automatic low power mode setting

- Remote differential feedback voltage sensing

- Vout range = 0.3~1.19375V with 6.25 mV per step, DVS through compatible interface or SRCLKEN pin

- SPMI or I2C-compatible interface which supports high-speed modes in 5G modem application field

- Selectable interface (SPMI/I2C) by eFuse

- Dedicated FAULTB pin to report fault alarm to main PMIC

- Chip enable pin for on/off control

- Output short circuit and input over-voltage protection

- Over-temperature protection

- Input under-voltage lockout (UVLO)

- 45-pin 2.35×3.44 mm WLCSP package

#### 1.2 **Applications**

- Smart phones, eBooks and tablets, mobile phones and Ultrabooks

- Handsets, gaming devices, car infotainment

- TV and media players

- Industrial HMI, desktop POS, KIOSK, digital signage

#### 1.3 **General Description**

The MT6319 is designed to meet the power management requirements of the latest applications processors in mobile phones and similar portable applications.

The device contains four step-down DC/DC converters, which are bundled together in 4-phase buck converter and can be configured into various phase configurations by eFuse to power any application requirement.

The device is fully controlled by SPMI interface or an I2C compatible serial interface.

The MT6319 focuses on high-efficiency, step-down conversion over a wide output current range. The step-down converter enters the low power mode at light load for maximum efficiency. The regulator supports remote differential voltage sensing to compensate I\*R drop between the regulator output and the load.

The protection features include short-circuit protection, output under voltage protection (power good function), input OVP, UVLO and temperature warning and shutdown functions.

Several fault flags are provided for status information of the IC.

During startup, the device controls the output slew rate to minimize output voltage overshoot and the inrush current.

The MT6319 is available in a 45-pin WLCSP package. The operating temperature ranges from -30°C to +85°C.

### 1.4 Ordering Information

Table 1-1. Ordering option

| Order #    | Marking | Temp. range | Package   |

|------------|---------|-------------|-----------|

| MT6319LP/A |         | -30 ~ +85°C | WLCSP 45L |

## **1.5** Part Voltage Table

Table 1-2. Part voltage table

| Top marking (1) | Default voltage (V) | Imax <sup>(2)</sup><br>(mA) | Default on (Y/N) | Configuration | Lo      | Application |

|-----------------|---------------------|-----------------------------|------------------|---------------|---------|-------------|

| MT6319LP/A      | 0.75                | 5,000*2                     | Υ                | VBUCK1        | 0.24 uH | СРИВ        |

|                 |                     |                             |                  | VBUCK2        | 0.24 uH |             |

|                 | 1.125               | 5,000                       | Υ                | VBUCK3        | 0.24 uH | VDD2        |

|                 | 0.6                 | 5,000                       | Υ                | VBUCK4        | 0.24 uH | VDDQ        |

<sup>(1)</sup> Note 1 The parts top marking (LP) interface is used by SPMI only.

<sup>(2)</sup> Note 2 Imax for multi-phase configurations should consider the over-temperature protection possibility since they are hosted in a tiny package.

#### **Pin Assignment and Description** 1.6

| #1 | 1          | 2       | 3       | 4       | 5      | 6     |   |

|----|------------|---------|---------|---------|--------|-------|---|

| Α  | PVDD2      | VBUCK2  | PGND2   | PGND1   | VBUCK1 | PVDD1 | Α |

| В  | PVDD2      | VBUCK2  | PGND2   | PGND1   | VBUCK1 | PVDD1 | В |

| С  |            |         |         |         |        | INT   | с |

| D  | AV         | VFBP2   | VFBN2   | FAULTB  | VFBN1  | VFBP1 | D |

| Е  | DVDD18     | FSOURCE | SRCLKEN | WDTRSTB | SCLK   | SDAT  | E |

| F  | AG         | VFBP4   | VFBN4   | EN      | VFBN3  | VFBP3 | F |

| G  | DVDD18_VIO |         |         |         |        | RSV1  | G |

| н  | PVDD4      | VBUCK4  | PGND4   | PGND3   | VBUCK3 | PVDD3 | н |

| J  | PVDD4      | VBUCK4  | PGND4   | PGND3   | VBUCK3 | PVDD3 | J |

|    | 1          | 2       | 3       | 4       | 5      | 6     |   |

Figure 1-1. MT6319 WLCSP 45L (2.35×3.44 mm) pin assignment

Table 1-3. MT6319 pin description

| Ball         | Symbol     | I/O        | Description                                                |

|--------------|------------|------------|------------------------------------------------------------|

| A5, B5       | VBUCK1     | 0          | Switching node for buck 1                                  |

| A2, B2       | VBUCK2     | 0          | Switching node for buck 2                                  |

| H5, J5       | VBUCK3     | 0          | Switching node for buck 3                                  |

| H2, J2       | VBUCK4     | 0          | Switching node for buck 4                                  |

| A6, B6       | PVDD1      | PWR        | Power input for buck 1, to be connected to VSYS            |

| A1, B1       | PVDD2      | PWR        | Power input for buck 2, to be connected to VSYS            |

| H6, J6       | PVDD3      | PWR        | Power input for buck 3, to be connected to VSYS            |

| H1, J1       | PVDD4      | PWR        | Power input for buck 4, to be connected to VSYS            |

| D1           | AV         | PWR        | Analog input for buck, to be connected to VSYS             |

| G1           | DVDD18_VIO | PWR        | Power to SPMI I/O, to make slave/master use the same power |

| A4, B4       | PGND1      | Power GND  | Ground of power 1                                          |

| A3, B3       | PGND2      | Power GND  | Ground of power 2                                          |

| H4, J4       | PGND3      | Power GND  | Ground of power 3                                          |

| H3, J3       | PGND4      | Power GND  | Ground of power 4                                          |

| F1           | AG         | Analog GND | Ground of analog                                           |

| E1           | DVDD18     | PWR        | Digital power 1.8V                                         |

| D6           | VFBP1      | _          | BUCK1 positive feedback                                    |

| D5           | VFBN1      | _          | BUCK1 negative ground feedback                             |

| D2           | VFBP2      | _          | BUCK2 positive feedback                                    |

| D3           | VFBN2      | Ι          | BUCK2 negative ground feedback                             |

| F6           | VFBP3      | -          | BUCK3 positive feedback                                    |

| F5           | VFBN3      | _          | BUCK3 negative ground feedback                             |

| F2           | VFBP4      | _          | BUCK4 positive feedback                                    |

| F3           | VFBN4      | _          | BUCK4 negative ground feedback                             |

| F4           | EN         | _          | Chip enable pin                                            |

| E3           | SRCLKEN    | _          | Sleep control input                                        |

| E4           | WDTRSTB    | _          | Watchdog reset input                                       |

| E5           | SCLK       | 10         | SPMI/I2C clock                                             |

| E6           | SDAT       | 10         | SPMI/I2C data                                              |

| C6           | INT        | 0          | Interrupt output                                           |

| D4           | FAULTB     | 0          | Fault alarm signal                                         |

| E2           | FSOURCE    | Ι          | eFuse power for programming                                |

| G6           | RSV1       | 0          | For analog test                                            |

| C1~C5, G2~G5 | NC         |            |                                                            |

## **2** Electrical Characteristics

### 2.1 Absolute Maximum Ratings over Operating Free-Air Temperature Range

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device. These numbers are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2-1. Absolute maximum ratings

| Parameter                        | Condition           | Min.  | Typical | Max.          | Unit |

|----------------------------------|---------------------|-------|---------|---------------|------|

| Free-air temperature range       |                     | -40   |         | 85            | °C   |

| Storage temperature range        |                     | -65   |         | 150           | °C   |

| Datton, nin innut (1)            | Steady state        | -0.5  |         | 6             | V    |

| Battery pin input <sup>(1)</sup> | Transient (< 10 ms) | -0.5  |         | 6             | V    |

| Non-battery power pin (2)        | Steady state        | -0.5  |         | 5             | V    |

| Signal pin (3)                   | Steady state        | -0.5  |         | Vxx + 0.5 (3) | V    |

| ESD robustness                   | НВМ                 | 2,000 |         |               | V    |

- (1) Note 1 VSYS\_XXX/Vxxx (BUCK SW node)/VSYSSNS/BATADC -> battery input pin

- (2) Note 2 Non-battery power input -> refer to Table 2-1 (PWR pin but not connected with battery)

- (3) Note 3 Vxx = Max. operation voltage (refer to Table 2-2)

### 2.2 Thermal Characteristics

Table 2-2. Thermal Characteristics

| Parameter                                                      | Condition   | Min. | Typical | Max. | Unit |

|----------------------------------------------------------------|-------------|------|---------|------|------|

| Thermal resistance from junction to ambient (O <sub>JA</sub> ) | In free air |      | 43.9    |      | °C/W |

Note. The device is mounted on a 4-metal-layer PCB and modeled per JEDEC51-7 condition.

## 2.3 Pin Voltage Range

The table below lists the operating voltage ranges for all MT6319 I/O pins.

Table 2-3. Pin voltage range

| Ball   | Symbol     | Voltage range | Unit |

|--------|------------|---------------|------|

| A5, B5 | VBUCK1     | 0~5           | V    |

| A3, B3 | VBUCK2     | 0~5           | V    |

| H5, J5 | VBUCK3     | 0~5           | V    |

| ·      | VBUCK4     | 0~5           | V    |

| H2, J2 |            |               | V    |

| A6, B6 | PVDD1      | 0~5           | -    |

| A1, B1 | PVDD2      | 0~5           | V    |

| H6, J6 | PVDD3      | 0~5           | V    |

| H1, J1 | PVDD4      | 0~5           | V    |

| D1     | AV         | 0~5           | V    |

| G1     | DVDD18_VIO | 0~1.8         | V    |

| A4, B4 | PGND1      | 0             | V    |

| A3, B3 | PGND2      | 0             | V    |

| H4, J4 | PGND3      | 0             | V    |

| H3, J3 | PGND4      | 0             | V    |

| F1     | AG         | 0             | V    |

| E1     | DVDD18     | 0~1.8         | V    |

| D6     | VFBP1      | 0~5           | V    |

| D5     | VFBN1      | 0             | V    |

| D2     | VFBP2      | 0~5           | V    |

| D3     | VFBN2      | 0             | V    |

| F6     | VFBP3      | 0~5           | V    |

| F5     | VFBN3      | 0             | V    |

| F2     | VFBP4      | 0~5           | V    |

| F3     | VFBN4      | 0             | V    |

| F4     | EN         | 0~5           | V    |

| E3     | SRCLKEN    | 0~1.8         | V    |

| E4     | WDTRSTB    | 0~1.8         | V    |

| E5     | SCLK       | 0~1.8         | V    |

| E6     | SDAT       | 0~1.8         | V    |

| C6     | INT        | 0~1.8         | V    |

| D4     | FAULTB     | 0~5           | V    |

| E2     | FSOURCE    | 0~7.5         | V    |

| G6     | RSV1       | 0~5           | V    |

| •      | 1.011      | 0 0           | •    |

## 2.4 Recommended Operating Range

Table 2-4. Operation condition

| Parameter                   | Condition | Min. | Typical | Max. | Unit |

|-----------------------------|-----------|------|---------|------|------|

| Operating temperature range |           | -30  |         | 85   | °C   |

#### 2.5 **Electrical Characteristics**

VBAT = 2.5~5V, minimum loads applied on all outputs, unless otherwise noted Typical values are at TA = 25°C.

Table 2-5. General electrical specifications

| Parameter                         | Condition                                          | Min.      | Typical | Max.     | Unit   |  |

|-----------------------------------|----------------------------------------------------|-----------|---------|----------|--------|--|

| Operation ground current          |                                                    |           |         |          |        |  |

| Standby (one buck on)             | Low power mode<br>Chip_EN = High<br>Buck_EN = High |           | 304.5   | 358      | μΑ     |  |

| Standby (all bucks off)           | Low power mode<br>Chip_EN = High<br>Buck_EN = Low  |           | 13      | 17.5     | μΑ     |  |

| Off mode                          | Chip_EN = Low                                      |           |         | 1        | μΑ     |  |

| Under voltage (UV)                | Under voltage (UV)                                 |           |         |          |        |  |

| Under voltage falling threshold   |                                                    |           | 2.4     |          | V      |  |

| Under voltage rising threshold    |                                                    |           | 2.65    |          | V      |  |

| Over voltage lockout (OVLO)       |                                                    |           |         |          |        |  |

| Over voltage rising threshold     |                                                    | 5.7       | 5.8     | 5.9      | V      |  |

| EN                                |                                                    |           |         |          |        |  |

| High voltage                      |                                                    | 1.41      |         |          | V      |  |

| Low voltage                       |                                                    |           |         | 0.9      | V      |  |

| Control input voltage (SCLK, SDAT | , SRCLKEN related)                                 |           |         |          |        |  |

| Control input high                |                                                    | 0.75*DVDD |         |          | V      |  |

| Control input low                 |                                                    |           |         | 0.25*VIO | V      |  |

| Thermal shutdown                  |                                                    |           |         |          |        |  |

| PMIC shutdown threshold           |                                                    |           | 150     |          | degree |  |

## 3 MT6319 Packaging

## 3.1 Package Dimensions

Package: WLCSP 45L

Figure 3-1. Package dimensions

## **Exhibit 1 Terms and Conditions**

Your access to and use of this document and the information contained herein (collectively this "Document") is subject to your (including the corporation or other legal entity you represent, collectively "You") acceptance of the terms and conditions set forth below ("T&C"). By using, accessing or downloading this Document, You are accepting the T&C and agree to be bound by the T&C. If You don't agree to the T&C, You may not use this Document and shall immediately destroy any copy thereof.

This Document contains information that is confidential and proprietary to MediaTek Inc. and/or its affiliates (collectively "MediaTek") or its licensors and is provided solely for Your internal use with MediaTek's chipset(s) described in this Document and shall not be used for any other purposes (including but not limited to identifying or providing evidence to support any potential patent infringement claim against MediaTek or any of MediaTek's suppliers and/or direct or indirect customers). Unauthorized use or disclosure of the information contained herein is prohibited. You agree to indemnify MediaTek for any loss or damages suffered by MediaTek for Your unauthorized use or disclosure of this Document, in whole or in part.

MediaTek and its licensors retain titles and all ownership rights in and to this Document and no license (express or implied, by estoppels or otherwise) to any intellectual propriety rights is granted hereunder. This Document is subject to change without further notification. MediaTek does not assume any responsibility arising out of or in connection with any use of, or reliance on, this Document, and specifically disclaims any and all liability, including, without limitation, consequential or incidental damages.

THIS DOCUMENT AND ANY OTHER MATERIALS OR TECHNICAL SUPPORT PROVIDED BY MEDIATEK IN CONNECTION WITH THIS DOCUMENT, IF ANY, ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE. MEDIATEK SPECIFICALLY DISCLAIMS ALL WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, COMPLETENESS OR ACCURACY AND ALL WARRANTIES ARISING OUT OF TRADE USAGE OR OUT OF A COURSE OF DEALING OR COURSE OF PERFORMANCE. MEDIATEK SHALL NOT BE RESPONSIBLE FOR ANY MEDIATEK DELIVERABLES MADE TO MEET YOUR SPECIFICATIONS OR TO CONFORM TO A PARTICULAR STANDARD OR OPEN FORUM.

Without limiting the generality of the foregoing, MediaTek makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does MediaTek assume any liability arising out of the application or use of any product, circuit or software. You agree that You are solely responsible for the designing, validating and testing Your product incorporating MediaTek's product and ensure such product meets applicable standards and any safety, security or other requirements.

The above T&C and all acts in connection with the T&C or this Document shall be governed, construed and interpreted in accordance with the laws of Taiwan, without giving effect to the principles of conflicts of law.