# MT6360P Power Management IC Product Brief

Version: 1.0 Release date: 202

2023-09-18

### The full datasheet is available with an NDA

Use of this document and any information contained therein is subject to the terms and conditions set forth in Exhibit 1. This document is subject to change without notice.

## **Version History**

| Version | Date       | Description      |

|---------|------------|------------------|

| 1.0     | 2023-09-18 | Official release |

## **Table of Contents**

| Vers   | n History ·····                      | ·· 2 |

|--------|--------------------------------------|------|

| Table  | of Contents                          | 3    |

| List o | Figures                              | 3    |

| List o | Tables ·····                         | 3    |

| 1      | Dverview ·····                       |      |

|        | .1 Features                          |      |

|        | .2 Applications                      | 5    |

|        | .3 General Description               | 5    |

|        | .4 Ordering Information              | 6    |

|        | .5 Pin Assignments and Description   | ·· 7 |

| 2      | lectrical Characteristics ·····      | 11   |

|        | .1 Absolute Maximum Ratings          | 11   |

|        | .2 Recommended Operating Range       | 11   |

|        | .3 Electrical Characteristics        | 12   |

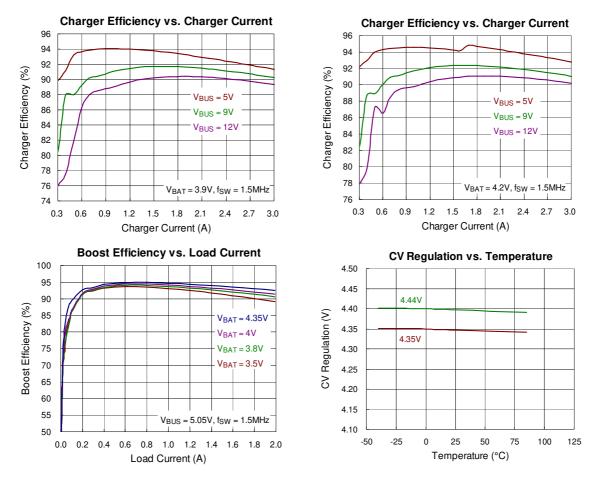

| 3      | ypical Operating Characteristics     | 25   |

|        | .1 Typical Operating Characteristics | 25   |

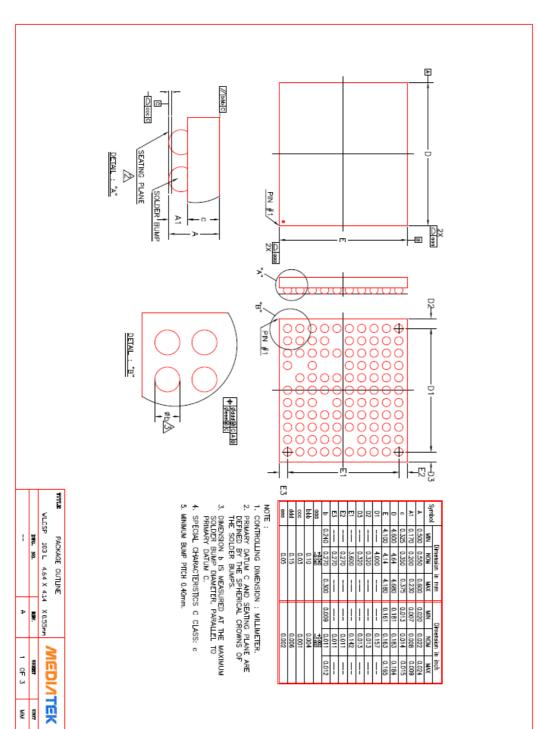

| 4      | AT6360P Packaging ·····              | 26   |

|        | .1 Outline Dimensions                |      |

| Exhi   | t 1 Terms and Conditions             | 28   |

## **List of Figures**

| Figure 1-1. Ordering information                           | 6 |

|------------------------------------------------------------|---|

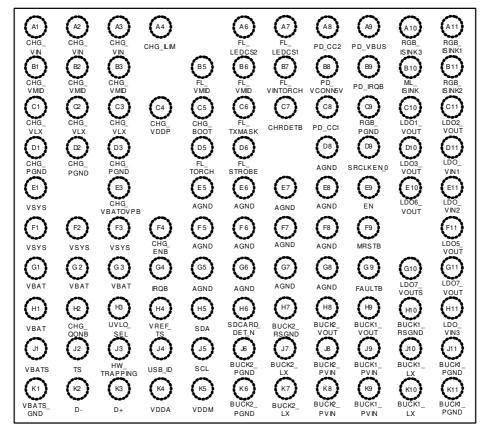

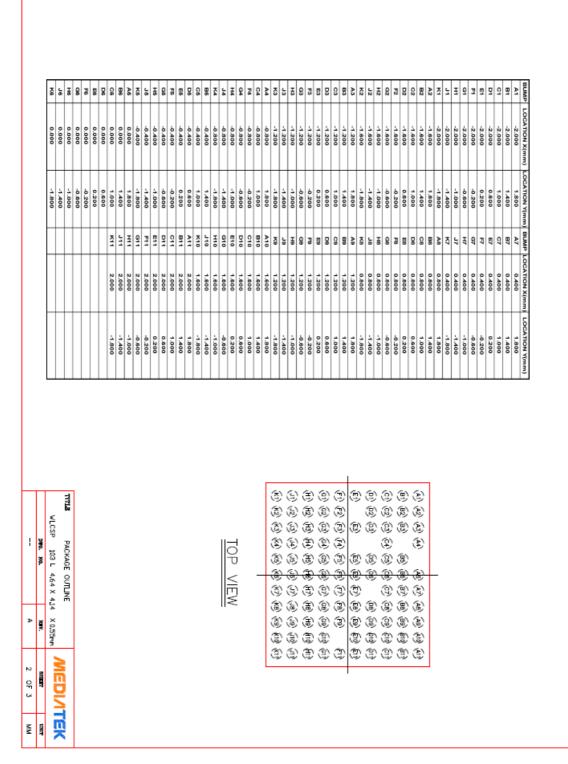

| Figure 1-2. MT6360P WL-CSP-103B 4.64×4.14 (BSC) (top view) | 7 |

| Figure 3-1. Typical operating characteristics              |   |

| Figure 4-1. Package dimension                              |   |

## **List of Tables**

| Table 1-1. MT6360P pin description   | .8 |

|--------------------------------------|----|

| Table 2-1. Absolute maximum ratings  | .1 |

| Table 2-2. Electrical specifications | .2 |

## **1** Overview

### **1.1** Features

### • Battery charger

- High-accuracy voltage/current regulation

- Average input current regulation (AICR): 0.1~3.25A in 50 mA steps

- Charge current regulation accuracy: ±5%

- Charge voltage regulation accuracy: ±0.5% (0~70°C)

- Synchronous 1.5 MHz fixed-frequency PWM controller with up to 95% duty cycle

- Thermal regulation and protection

- Over-temperature protection

- Input over-voltage protection

- $\,-\,$  IRQ output for communication via  $I^2C$

- Automatic charging

- BATFET control to support ship mode, wake-up, and full system reset

- Resistance compensation from charger output to cell terminal

- USB OTG output voltage range: 4.85~5.825V

- D+/D- detection for BC1.2

- Micro-B ID pin rust

- Integrated ADCs for system monitoring (charger current, voltage, and temperature)

- Low battery protection from 2.7V to 3.8V for boost operation

- Initial VOREG set for relieve battery protection

- USB\_PD

- PD-compatible dual-role

- Attach/Detach detection as host, device or dual-role port

- Current capability definition and detection

- Cable recognition

- Supports alternate mode

- Supports VCONN with programmable over-current protection (OCP)

- Supports dead battery

- Supports BIST mode

- USB PD3.0

- Flash LED driver

- Synchronous boost dual flash LED driver with dual independently-programmable LED current sources

- Torch mode current: 25~400 mA in 12.5 mA steps per channel

- I<sup>2</sup>C-programmable flash safety timer, from 64 ms to 2,432 ms with 32 ms/step

- Flash LED1/LED2 short-circuit protection; output short-circuit protection

- TXMask protection with dedicated FL\_TXMASK pin

- Shared charger/OTG as power stage

- Independent torch bypass MOSFET from VSYS

- Strobe mode current: 50 mA ~ 1.5A in 12.5 mA steps or 25~750 mA in 6.25 mA steps per channel; up to 2.5A in total

- LDO

- 6-channel LDO

- LDO1 output current: 150 mA

- LDO2/3 output current: 200 mA

- LDO5 output current: 800 mA

- LDO6 output current: 300 mA

- LDO7 output current: 600 mA

- **RGB LED driver**

- 3-channel LED driver

- Sink current for 3 RGB LEDs: 24 mA/channel

- Flash mode frequency range: 0.125~256 Hz

- RGB\_ISINK1 for CHG\_VIN power food indicator

- Supports register mode, flash mode, breath mode

- **Moonlight LED driver**

- 5~150 mA sink type LED driver

- Linear mode control

- 5 mA/Step

- Buck

- 2-channel buck

- 0.3~1.3V programmable slew rate for voltage transitions

- Output current capability: 3A

- Supports sequenced off delay time selection

- Input under-voltage lockout (UVLO)

- Thermal shutdown and overload protection

#### 1.2 **Applications**

- Cellular telephones

- Personal information appliances

- Tablet PCs

- Portable instruments

- Industrial HMI, desktop POS, KIOSK, digital signage

#### 1.3 **General Description**

MT6360P is a highly-integrated smart power management IC which includes a single cell Li-Ion/Li-Polymer switching battery charger, a USB Type-C and power delivery (PD) controller, dual flash LED current sources, a RGB LED driver, two buck converters, and six LDOs for portable devices.

The switching charger integrates a synchronous PWM controller, power MOSFETs, input current sensing and input current regulation, high-accuracy voltage regulation, and charge termination circuitry. Besides, the charge current is regulated through the integrated sensing resistors. It also features USB on-the-go (OTG) support.

The USB Type-C and PD controller complies with the latest USB Type-C and PD standards. It integrates a complete Type-C transceiver including the Type-C termination resistors, Rp and Rd, and enables the USB Type-C detection including attach and orientation. It also integrates the physical layer of the USB BMC power delivery protocol, allowing power transfers and role swaps. The BMC PD function provides full support for alternate modes on the USB Type-C standard.

Dual independent current sources supply for each flash LED. The power for the current sources in strobe mode are from the CHG VMID pin, which is supplied from the charger in reverse boost mode, the same operation as OTG mode of the charger. The high-side current sources, allowing for grounded-cathode connection for LEDs, provide strobe mode current levels from 50 mA to 1.5A in a 12.5 mA step or from 25 mA to 750 mA in a 6.25 mA step, and torch mode current levels from 25 mA to 400 mA in a 12.5mA step. The two channels is able to support totally up to 2.5A.

The dual buck converter delivers a digitally programmable output 0.3V to 1.3V from an input voltage supply of 2.5V to 5.5V. The output voltage is programmed through an I<sup>2</sup>C interface capable of operating up to 3.4 MHz.

By using a proprietary architecture with synchronous rectification, BUCK1/2 are capable of delivering 3A continuously as PVIN > 3.1V.

LDO1 supplies power to finger print unit (VFP); LDO2 supplies power to the touch panel unit (VTP); LDO3 and LDO5 supply power to SD card and UFS card (VMC and VMCH); LDO6 and LDO7 supply power to DRAM (VMDDR and VDRAM2). These are in mobile phones and other hand-held devices. The output voltage is programmable via the I<sup>2</sup>C interface.

The RGB LED driver is a 3-channel smart LED string controller to drive three channels of LEDs with a sink current of up to 24 mA and a CHG VIN power good indicator with a sink current of up to 24 mA. All channels can be set independently via the I<sup>2</sup>C interface and are provided with three operation modes, register mode, flash mode and breath mode.

MT6360P is available in a WL-CSP-103B 4.64×4.14 (BSC) package.

#### 1.4 **Ordering Information**

MT6360 P 1/A Package Type P:WL-CSP-103B4.64x4.14 (BSC)

Figure 1-1. Ordering information

#### **Pin Assignments and Description** 1.5

Figure 1-2. MT6360P WL-CSP-103B 4.64×4.14 (BSC) (top view)

|            | Table 1-1. MT6360P pin description |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin no.    | Pin name                           | Pin description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| A1, A2, A3 | CHG_VIN                            | Charger power input                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| A4         | CHG_ILIM                           | Input current limit setting pin<br>A resistor is connected from CHG_ILIM pin to ground to set up the<br>maximum input current limit. The actual input current limit is the<br>lower value set through the CHG_ILIM pin and IAICR register bits.                                                                                                                                                                  |  |  |  |  |  |

| A6         | FL_LEDCS2                          | High-side current source output 2 for flash LED2                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| A7         | FL_LEDCS1                          | High-side current source output 1 for flash LED1                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| A8         | PD_CC2                             | Type-C connector configuration channel (CC) 2<br>This is used to detect a cable plug event and determine the cable<br>orientation.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| A9         | PD_VBUS                            | CHRDETB detection and VBUS input for attach and detach detection when the device operates as an UFP port                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| A10        | RGB_ISINK3                         | RGB LED current sink output 3                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| A11        | RGB_ISINK1                         | RGB LED current sink output 1                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| B1, B2, B3 | CHG_VMID                           | Connection point between the reverse-blocking MOSFET and the<br>high-side switching MOSFET                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| B5, B6     | FL_VMID                            | Flash LED driver power input for strobe mode<br>Connect a 4.7μF ceramic capacitor between FL_VMID and ground.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| В7         | FL_VINTORCH                        | Flash LED driver power input for torch mode                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| B8         | PD_VCONN5V                         | Regulated input voltage to power PD_CC pins as VCONN                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| В9         | PD_IRQB                            | Active-low open-drain interrupt output<br>This requests the processor to check the registers.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| B10        | ML_ISINK                           | Moonlight LED current sink output                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| B11        | RGB_ISINK2                         | RGB LED current sink output 2                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| C1, C2, C3 | CHG_VLX                            | Charger switch node for output inductor connection                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| C4         | CHG_VDDP                           | <ul> <li>Regulated output voltage to supply for the PWM low-side gate driver and the bootstrap capacitor</li> <li>Connect a 2.2µF ceramic capacitor between CHG_VDDP and ground.</li> <li>1. If VBUS is plugged in, CHG_VDDP will be powered by</li> <li>CHG_VIN and regulated to 4.9V.</li> <li>2. If VBUS is unplugged, the charger will operate in sleep mode and the CHG_VDDP voltage will be 0V.</li> </ul> |  |  |  |  |  |

| C5         | CHG_BOOT                           | Charger bootstrap voltage to supply the high-side MOSFET gate driver<br>Connect a capacitor between CHG_BOOT and CHG_VLX.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| C6         | FL_TXMASK                          | Configurable power amplifier synchronization input or configurable<br>active-high torch mode enable<br>Connect a 300kΩ internal pull-down resistor between FL_TXMASK<br>and ground.                                                                                                                                                                                                                              |  |  |  |  |  |

| C7         | CHRDETB                            | CHG_VIN ready indication, open-drain output that indicates<br>PD_VBUS is in                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| C8         | PD_CC1                             | Type-C connector configuration channel (CC) 1<br>This is used to detect a cable plug event and determine the cable<br>orientation.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| С9         | RGB_PGND                           | RGB ground<br>Tie RGB_PGND and ground on the PCB.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| C10        | LDO1_VOUT                          | LDO1 output                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| C11        | LDO2_VOUT                          | LDO2 output                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| D1, D2, D3 | CHG PGND                           | Charger ground                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

### Table 1-1, MT6360P pin description

| Pin no.                 | Pin name     | Pin description                                                                                                  |

|-------------------------|--------------|------------------------------------------------------------------------------------------------------------------|

|                         |              | Tie CHG_PGND and ground on the PCB.                                                                              |

| D5                      | FL_TORCH     | Flash LED torch mode enable input                                                                                |

| D6                      | FL STROBE    | Flash LED strobe mode enable input                                                                               |

| D8, E5, E6, E7, E8, F5, | _            |                                                                                                                  |

| F6, F7, F8, G5, G6, G7, | AGND         | Analog ground                                                                                                    |

| G8                      |              | Tie AGND and ground on the PCB.                                                                                  |

| D9                      | SRCLKEN_0    | Source clock enable on and LP control pin 0                                                                      |

| D10                     | LDO3_VOUT    | LDO3 output                                                                                                      |

| D11                     | LDO_VIN1     | LDO_VIN1 power input for LDO1, LDO2 and LDO3                                                                     |

|                         |              | Connect a $2.2 \mu F$ ceramic capacitor between LDO_VIN1 and ground.                                             |

|                         |              | System connection node                                                                                           |

| E1, F1, F2, F3          | VSYS         | Internal BATFET is connected between VSYS and VBAT. Connect a                                                    |

|                         |              | 22μF ceramic capacitor between VSYS and ground.                                                                  |

|                         |              | Battery over-voltage protection (BAT OVP) indication                                                             |

| E3                      | CHG_VBATOVPB | This is an open-drain and active-low output. It will be low if BAT OVP                                           |

|                         |              | occurs; otherwise, it is high.                                                                                   |

| E9                      | EN           | BUCK1, BUCK2, LDO6 and LDO7 enable control input                                                                 |

|                         |              | When EN = low, all bucks and LDOs are turned off.                                                                |

| E10                     | LDO6_VOUT    | LDO6 output                                                                                                      |

| E11                     | LDO_VIN2     | LDO_VIN2 power input for LDO5 and logic circuit of LDO6/7                                                        |

|                         |              | Connect a 2.2µF ceramic capacitor between LDO_VIN2 and ground.                                                   |

| F4                      | CHG_ENB      | Charger enable input, active-low                                                                                 |

| F9                      | MRSTB        | Manual reset input for hardware reset                                                                            |

| F11                     | LDO5_VOUT    | LDO5 output                                                                                                      |

|                         |              | Charge current output node for battery connection                                                                |

| G1, G2, G3, H1          | VBAT         | The internal BATFET is connected between VSYS and VBAT. Connect a                                                |

|                         |              | 10μF ceramic capacitor between VBAT and ground.                                                                  |

| G4                      | IRQB         | Active-low open-drain interrupt output                                                                           |

|                         |              | This requests the processor to read the registers.                                                               |

| G9                      | FAULTB       | Indicates power not good of bucks and LDOs                                                                       |

| C10                     |              | Active-low open-drain                                                                                            |

| G10                     | LDO7_VOUTS   | LDO7 output voltage-sense input                                                                                  |

| G11                     | LDO7_VOUT    | LDO7 output                                                                                                      |

| Н2                      | CHG QONB     | Internal BATFET enable control input                                                                             |

| пг                      |              | In shipping mode, CHG_QONB is pulled low for the duration of tSHIPMODE_CHG (typical 0.9s) to exit shipping mode. |

|                         |              | SYSUVLO rising threshold voltage setting and the UVLO_SEL pin                                                    |

| Н3                      | UVLO_SEL     | defines default value                                                                                            |

| H4                      | VREF_TS      | Power output of 1.8V reference power for temperature sensing                                                     |

|                         | _            | I <sup>2</sup> C interface serial data input/output                                                              |

| H5                      | SDA          | Open-drain. An external pull-up resistor is required.                                                            |

| H6                      | SDCARD_DET_N | When SDCARD_DET_N is active, disable LDO5.                                                                       |

| H7                      | BUCK2_RSGND  | BUCK2 remote sense ground                                                                                        |

| H8                      | BUCK2_VOUT   | BUCK2 output voltage sense through this pin                                                                      |

| H9                      | BUCK1_VOUT   | BUCK1 output voltage sense through this pin                                                                      |

| H10                     | BUCK1_RSGND  | BUCK1 remote sense ground                                                                                        |

|                         |              | LDO_VIN3 power input for LDO6 and LDO7                                                                           |

| H11                     | LDO_VIN3     | Connect a $2.2\mu$ F ceramic capacitor between LDO_VIN3 and ground.                                              |

| J1                      | VBATS        | Battery voltage-sense                                                                                            |

| 77                      | VDAIS        | Battery voltage-sense                                                                                            |

| Pin no.  | Pin name    | Pin description                                                                                                                              |  |  |  |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| J2       | TS          | Temperature-sense input, connected to a resistor divider for temperature programming                                                         |  |  |  |

| J3       | HW_TRAPPING | Either uses an external pull-down resistor or connects the pin to VDDA to define power configuration                                         |  |  |  |

| J4       | USB_ID      | USB ID port connected to USB receptacle                                                                                                      |  |  |  |

| J5       | SCL         | I <sup>2</sup> C interface serial clock input<br>Open-drain. An external pull-up resistor is required.                                       |  |  |  |

| J6, K6   | BUCK2_PGND  | BUCK2 power ground<br>The low-side MOSFET is referenced to this pin. CIN and COUT should<br>be returned with a minimal path to these pins.   |  |  |  |

| J7, K7   | BUCK2_LX    | BUCK2 switching node<br>Connect to the inductor.                                                                                             |  |  |  |

| J8, K8   | BUCK2_PVIN  | BUCK2 power input voltage<br>Connect to the input power source. Connect to CIN with minimal<br>path.                                         |  |  |  |

| Ј9, К9   | BUCK1_PVIN  | BUCK1 power input voltage<br>Connect to the input power source. Connect to CIN with minimal<br>path.                                         |  |  |  |

| J10, K10 | BUCK1_LX    | BUCK1 switching node<br>Connect to the inductor.                                                                                             |  |  |  |

| J11, K11 | BUCK1_PGND  | BUCK1 power ground<br>The low-side MOSFET is referenced to this pin. CIN and COUT should<br>be returned with a minimal path to these pins.   |  |  |  |

| К1       | VBATS_GND   | Battery voltage-sense ground                                                                                                                 |  |  |  |

| К2       | D-          | USB D- port                                                                                                                                  |  |  |  |

| КЗ       | D+          | USB D+ port                                                                                                                                  |  |  |  |

| К4       | VDDA        | Regulated power input for an internal analog base<br>Connect a 2.2µF ceramic capacitor between VDDA and ground.                              |  |  |  |

| К5       | VDDM        | Regulated voltage output<br>Connect a 2.2μF ceramic capacitor between VDDM and PGND. It also<br>provides power to all VDDA-powered circuits. |  |  |  |

## 2 Electrical Characteristics

### 2.1 Absolute Maximum Ratings

#### Table 2-1. Absolute maximum ratings

(1)

| Parameter                                 | Condition                                    | Min. | Тур. | Max. | Unit |

|-------------------------------------------|----------------------------------------------|------|------|------|------|

| PD_VBUS                                   |                                              | -0.5 | -    | 28   | V    |

| PD_CC1, PD_CC2                            |                                              | -0.5 | -    | 24   | V    |

| Detter ric incut (4)                      | Steady state                                 | -0.5 | -    | 6    | V    |

| Battery pin input <sup>(4)</sup>          | Transient (< 10 ms)                          | -0.5 | -    | 7    | V    |

| CHG_VIN, CHG_VMID, CHG_BOOT, FL_VMID      |                                              | -0.5 | -    | 22   | V    |

| USB ID, D+, D-                            |                                              | -0.5 | -    | 24   | V    |

|                                           |                                              | -0.5 | -    | 16   | V    |

| CHG_LX                                    | LX (peak < 100 ns duration)                  | -    | -    | -2   |      |

| Other pins                                |                                              | -0.5 | -    | 6    | V    |

| Power dissipation, P <sub>D</sub>         | @TA = 25°C<br>WL-CSP-103B 4.64x4.14 (BSC)    | -    | -    | 4.44 | w    |

| Package thermal resistance <sup>(2)</sup> | WL-CSP-103B 4.64x4.14 (BSC), θ <sub>JA</sub> | -    | 22.5 | -    | °C/W |

| Lead temperature                          | Soldering, 10 sec.                           | -    | -    | 260  | °C   |

| Storage temperature range                 |                                              | -65  | -    | 150  | °C   |

| ESD susceptibility <sup>(3)</sup>         | HBM (human body model)                       | -    | -    | 2    | kV   |

(1) Note 1 Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

(2) Note 2  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}$  C with the component mounted on a high effective-thermalconductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

(3) Note 3 Devices are ESD sensitive. Handling precaution is recommended.

(4) Note 4 Battery input pin: VBAT/VBATS/VSYS/BUCKx\_PVIN/BUCKx\_LX/LDO\_VINx/FL\_VINTORCH

### 2.2 Recommended Operating Range

- PD\_VBUS, CHG\_VIN supply input voltage: 4~14V

- VBAT supply input voltage: 2.8~5V

- BUCK1/2\_PVIN input voltage: 3.1~5V

- LDO\_VIN1/2: 3.15~5V

- LDO\_VIN3: 1.1~5V

- IBAT (discharging current with internal MOSFET): 6A (continues)

- IBAT (discharging current with internal MOSFET): 9A (peak, up to 1 sec duration)

- Junction temperature range: -40~125°C

- Ambient temperature range: -40~85°C

Note. The device is not guaranteed to function outside its operating conditions.

#### 2.3 **Electrical Characteristics**

### V<sub>CHG\_VIN</sub> = 5V, V<sub>BAT</sub> = 4.2V, L1 = L2 = 0.33µH, L3 = 1µH, C2 = 2.2µF, C18 = 10µF, T<sub>A</sub> = 25°C, unless otherwise specified

| Parameter                                                     | Symbol                     | Test condition                                                                                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| PMIC quiescent current                                        | -                          |                                                                                                                                                                                                                                   |      |      |      |      |

| Shutdown current                                              | Ishdn                      | On VBAT pin, with all channels shut down, V <sub>BAT</sub> = 4V                                                                                                                                                                   | -    | 63   | 85   | μA   |

| Shipping-mode current                                         | IBAT_SHIP                  | VBAT only, in shipping mode                                                                                                                                                                                                       | -    | 16   | 40   | μA   |

| CHG_VIN supply<br>current                                     | Ichg_vin                   | $V_{CHG_VLX}$ is non-switching<br>$V_{CHG_VIN} = 5V$ , $V_{BAT} = V_{CV_CHG}$<br>ICHG = 0<br>Flash LED, LDOs, bucks and RGB<br>devices disabled, PD cable<br>attached (Full functions are not in<br>the communication situation.) | -    | 4.6  | 6.8  | mA   |

| CHG_VIN supply<br>current with charger in<br>H-Z mode         | Ichg_vin_hz                | $V_{CHG_VLX}$ is in high-impedance mode<br>$V_{CHG_VIN} = 5V$ , $V_{BAT} = 4V$<br>Flash LED, LDOs, bucks, PD and<br>RGB devices disabled                                                                                          | -    | 210  | 500  | μΑ   |

| Over-temperature<br>protection threshold                      | Тотр                       | Thermal shutdown threshold temperature                                                                                                                                                                                            | -    | 150  | -    | °C   |

| Over-temperature<br>protection accuracy                       | Totp_acc                   | Thermal shutdown temperature accuracy                                                                                                                                                                                             | -15  | -    | 15   | °C   |

| Over-temperature<br>protection recover                        | Totp_recover               | Thermal shutdown recover temperature                                                                                                                                                                                              | 95   | 110  | 125  | °C   |

| Control I/O pin, VDDA a                                       | nd VSYS                    |                                                                                                                                                                                                                                   |      |      |      |      |

| Logic-low threshold<br>voltage for all open-<br>drain outputs | Vol                        | I <sub>DS</sub> = 10 mA                                                                                                                                                                                                           | -    | -    | 0.4  | v    |

| Logic-high threshold voltage for all inputs                   | VIH                        | Logic-high threshold                                                                                                                                                                                                              | 1.2  | -    | -    | V    |

| Logic-low threshold voltage for all inputs                    | VIL                        | Logic-low threshold                                                                                                                                                                                                               | -    | -    | 0.4  | V    |

| SYS under-voltage<br>protection rising<br>threshold range     | Vsys_uvlo_rise             | External R selection<br>R = 1 M $\Omega$ (2.9V), 100 mV/step                                                                                                                                                                      | 2.8  | -    | 3.3  | V    |

| SYS under-voltage<br>protection rising<br>threshold accuracy  | $V_{SYS\_UVLO\_ACC\_RISE}$ | V <sub>SYS</sub> rising, default 2.9V                                                                                                                                                                                             | -50  | -    | +50  | mV   |

| De-bouncing time by<br>SYS UVLO rising                        | tdeboun_sys_uvlo_rise      |                                                                                                                                                                                                                                   | -    | 15   | -    | ms   |

| SYS under-voltage<br>protection falling<br>threshold range    | Vsys_uvlo_fall             | l <sup>2</sup> C programmable, default 2.5V, 50<br>mV/step                                                                                                                                                                        | 2.4  | -    | 2.8  | V    |

| SYS under-voltage<br>protection falling<br>threshold accuracy | Vsys_uvlo_acc_fall         | V <sub>SYS</sub> falling, default 2.5V                                                                                                                                                                                            | -50  | -    | +50  | mV   |

| VDDA over-voltage<br>protection threshold                     | Vvdda_ovp                  | V <sub>DDA</sub> rising                                                                                                                                                                                                           | 5.25 | 5.5  | 5.75 | v    |

### Table 2-2. Electrical specifications

| Parameter                                                       | Symbol                 | Test condition                                                                    | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| VDDA over-voltage                                               | Vvdda_ovp_hys          | V <sub>DDA</sub> falling                                                          | -    | 0.2  | -    | V    |

| protection hysteresis                                           | VDDA_OVP_HTS           | VDDA runnig                                                                       |      | 0.2  |      | v    |

| Pull-down ability on<br>MRSTB                                   | Ipd_mrstb              |                                                                                   | -    | 1    | 2.3  | μA   |

| Pull-down ability on<br>SDCARD_DET_N                            | Ipd_sdcard_det_n       |                                                                                   | -    | 1    | 2.3  | μΑ   |

| Pull-down resistance on<br>SRCLKEN_0                            | R <sub>SRCLKEN_0</sub> |                                                                                   | -    | 1    | 2.3  | μA   |

| Pull-down resistance on<br>EN                                   | R <sub>EN</sub>        |                                                                                   | -    | 350  | -    | kΩ   |

| USB ID                                                          |                        |                                                                                   |      |      |      |      |

|                                                                 |                        | V <sub>USB_ID</sub> = 0.6V, 0x6F[7] = 1                                           | 0.57 | 0.6  | 0.63 | V    |

| USB_ID pull-up voltage                                          | VUSB_ID_PULLUP         | $V_{USB_{ID}} = 1.8V, 0x6F[7] = 0$                                                | 1.71 | 1.8  | 1.89 | V    |

| USB_ID pull-up<br>resistance tolerance                          | Rusb_id_pullup         | 500 kΩ, 75 kΩ, 5 kΩ, 1 kΩ                                                         | -20  | _    | 20   | %    |

| USB_ID pull-down<br>resistance                                  | Rusb_id_pullup         | 500 kΩ, 75 kΩ, 5 kΩ, 1 kΩ                                                         | 3.75 | 5    | 6.25 | kΩ   |

| Interrupt threshold                                             |                        | 0x6F[6] = 0, 0x6F[7] = 0                                                          | 1.3  | 1.45 | 1.6  |      |

| voltage                                                         | VID_INT                | 0x6F[6] = 1, 0x6F[7] = 1                                                          | 0.18 | 0.2  | 0.22 | V    |

| Interrupt threshold                                             |                        | 0x6F[7] = 1                                                                       | -    | 0.05 | -    |      |

| voltage hysteresis                                              | Vid_int_hys            | 0x6F[7] = 0                                                                       | -    | 0.1  | -    | V    |

| Interrupt debounce<br>time tolerance                            | tid_int_deb            | I <sup>2</sup> C programmable,5 μs ~ 64 ms<br>(default 50 μs)                     | -10  | -    | 10   | %    |

| Input equivalent capacitance                                    | CID_IN_CAP             |                                                                                   | -    | -    | 20   | pF   |

| Charger                                                         |                        |                                                                                   |      |      |      |      |

| Sleep-mode entry<br>threshold                                   | Vsleep_enter_chg       | V <sub>CHG_VIN</sub> falling, V <sub>CHG_VIN</sub> - V <sub>BAT</sub>             | 0    | 0.04 | 0.1  | V    |

| Sleep-mode exit<br>threshold                                    | Vsleep_exit_chg        | V <sub>CHG_VIN</sub> rising, V <sub>CHG_VIN</sub> - V <sub>BAT</sub>              | 0.04 | 0.1  | 0.2  | v    |

| Sleep-mode exit<br>deglitch time                                | td_sleep_exit_chg      | Exit sleep-mode                                                                   | -    | 120  | -    | ms   |

| CHG_VIN bad adapter threshold                                   | VBAD_ADP_CHG           | V <sub>CHG_VIN</sub> falling                                                      | -    | 3.8  | -    | V    |

| CHG_VIN bad adapter<br>hysteresis                               | VBAD_ADP_HYS_CHG       | V <sub>CHG_VIN</sub> rising                                                       | -    | 150  | -    | mV   |

| CHG_VIN bad adapter sink current                                | Ibad_adp_sink_chg      |                                                                                   | -    | 50   | -    | mA   |

| CHG_VIN bad adapter detection time                              | tbad_adp_det_chg       |                                                                                   | -    | 30   | -    | ms   |

| Input current limit<br>factor                                   | K <sub>ILIM_CHG</sub>  | Input current regulation 508 mA by<br>CHG_ILIM pin with resistance =<br>698Ω      | 320  | 355  | 390  | AΩ   |

| CHG_VIN minimum<br>input voltage regulation<br>(MIVR) threshold | Vmivr_chg              | I <sup>2</sup> C programmable range in 0.1V steps                                 | 3.9  | -    | 13.4 | V    |

| CHG_VIN minimum<br>input voltage regulation<br>accuracy         | Vmivr_acc_chg          | V <sub>MIVR</sub> = 4.4V or 9V                                                    | -2   | -    | 2    | %    |

| AICR 100 mA mode                                                | IAICR_100mA_CHG        | I <sub>AICR</sub> = 100 mA, V <sub>CHG_VIN</sub> = 5V,<br>V <sub>BAT</sub> = 3.8V | 86   | 93   | 100  | mA   |

| Parameter                                         | Symbol                 | Test condition                                                                                                                       | Min.  | Тур.  | Max.  | Unit |

|---------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| AICR 500 mA mode                                  | IAICR_500mA_CHG        | I <sub>AICR</sub> = 500 mA, V <sub>CHG_VIN</sub> = 5V,<br>V <sub>BAT</sub> = 3.8V                                                    | 440   | 470   | 500   | mA   |

| AICR 1,000 mA mode                                | IAICR_1000mA_CHG       | I <sub>AICR</sub> = 1,000 mA, V <sub>CHG_VIN</sub> = 5V,<br>V <sub>BAT</sub> = 3.8V                                                  | 880   | 940   | 1,000 | mA   |

| AICR 1,500 mA mode                                | IAICR_1500mA_CHG       | I <sub>AICR</sub> = 1,500 mA, V <sub>CHG_VIN</sub> = 5V,<br>V <sub>BAT</sub> = 3.8V                                                  | 1,300 | 1,400 | 1,500 | mA   |

| CHG_VIN UVLO                                      | VUVLO_CHG              | V <sub>CHG_VIN</sub> rising                                                                                                          | 3.05  | 3.3   | 3.55  | V    |

| CHG_VIN UVLO<br>hysteresis                        | Vuvlo_hys_chg          | V <sub>CHG_VIN</sub> falling                                                                                                         | -     | 150   | -     | mV   |

| CHG_VIN over-voltage<br>protection threshold      | VCHG_VIN_OVP_CHG1      | V <sub>CHG_VIN</sub> rising, I <sup>2</sup> C programmable 5.5V                                                                      | 5.17  | 5.5   | 5.86  | V    |

| CHG_VIN over-voltage<br>protection threshold      | VCHG_VIN_OVP_CHG2      | V <sub>CHG_VIN</sub> rising, I <sup>2</sup> C programmable<br>6.5V (default)                                                         | 6.11  | 6.5   | 6.92  | V    |

| CHG_VIN over-voltage protection threshold         | Vchg_vin_ovp_chg3      | V <sub>CHG_VIN</sub> rising, I <sup>2</sup> C programmable<br>11V                                                                    | 10.34 | 11    | 11.71 | V    |

| CHG_VIN over-voltage protection threshold         | Vchg_vin_ovp_chg4      | V <sub>CHG_VIN</sub> rising, I <sup>2</sup> C programmable<br>14.5V                                                                  | 13.63 | 14.5  | 15.44 | V    |

| CHG_VIN over-voltage protection propagation delay | tchg_vin_ovp_ch        | V <sub>CHG_VIN</sub> rising above V <sub>CHG_VIN</sub> over-<br>voltage protection threshold turn<br>off UUG MOS, OVP setting = 6.5V | -     | 100   | -     | ns   |

| CHG_VIN over-voltage protection hysteresis        | Vchg_vin_ovp_hys_chg   | $V_{CHG_{VIN}}$ falling                                                                                                              | -     | 250   | -     | mV   |

| VBAT over-voltage protection threshold            | VBAT_OVP_CHG           | V <sub>BAT</sub> rising, as percentage of<br>V <sub>OREG_CHG</sub> , as V <sub>BAT</sub> /V <sub>OREG_CHG</sub> , 0x12[4]<br>TE = 0  | 106   | 108   | 110   | %    |

| VBAT over-voltage protection hysteresis           | Vbat_ovp_hys_chg       | V <sub>BAT</sub> falling, as (V <sub>BAT</sub> -<br>Voreg_chg)/Voreg_chg<br>0x12[4] TE = 0                                           | -     | 2     | -     | %    |

| Thermal regulation threshold                      | T <sub>THREG_CHG</sub> | Charge current starts decreasing (default)                                                                                           | -     | 120   | -     | °C   |

| VSYS over-voltage protection threshold            | Vsys_ovp_chg           | V <sub>SYS</sub> rising                                                                                                              | 4.9   | 5.25  | 5.5   | V    |

| VSYS under-voltage<br>protection threshold        | Vsys_uvp_chg           | Vsys falling                                                                                                                         | 2.2   | 2.4   | 2.6   | V    |

| VBAT depletion<br>threshold voltage               | VBAT_DPL_RISE          | V <sub>BAT_DPL</sub> rising                                                                                                          | 2.3   | 2.5   | 2.8   | V    |

| VBAT depletion<br>threshold voltage               | VBAT_DPL_FALL          | VBAT_DPL falling                                                                                                                     | 2     | 2.3   | 2.39  | V    |

| CHG_VIN force sleep<br>mode supply current        | ICHG_VIN_SLEEP         | Reg: 0x11[3] = 1                                                                                                                     | -     | -     | 2.5   | mA   |

| End of charge                                     |                        |                                                                                                                                      |       |       |       |      |

| Battery regulation voltage range                  | Voreg_chg              | I <sup>2</sup> C programmable in 10 mV steps                                                                                         | 3.9   | -     | 4.71  | V    |

| Battery regulation voltage accuracy               | Voreg_acc_chg          | $V_{OREG_{CHG}} = 4.2V, 4.35V, 4.36V, 4.37V, 4.38V, 4.43V or V_{OREG_{CHG}} = 4.45V (T_c = -10^{\circ} 70^{\circ}C)^{(3)}$           | -0.5  | -     | 0.5   | %    |

| Re-charge mode<br>threshold                       | Vrech_chg              | I <sup>2</sup> C programmable, V <sub>BAT</sub> falling,<br>difference below V <sub>OREG_CHG</sub>                                   | 50    | 100   | 150   | mV   |

| Re-charge deglitch time                           | td_rech_chg            | V <sub>BAT</sub> falling                                                                                                             | -     | 120   | -     | ms   |

| End-of-charge current                             | Іеос_снд               | I <sup>2</sup> C programmable in 50 mA steps                                                                                         | 100   | -     | 850   | mA   |

| Parameter                              | Symbol                   | Test condition                                                                               | Min.  | Тур. | Max.  | Unit |

|----------------------------------------|--------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|------|

| Default end-of-charge<br>current       | I <sub>EOC_DEF_CHG</sub> | Default                                                                                      | -     | 250  | -     | mA   |

| End-of-charge current accuracy         | I <sub>EOC_ACC</sub>     | I <sub>EOC_CHG</sub> = 150 mA, 200 mA, 250 mA                                                | -20   | -    | 20    | %    |

| End-of-charge deglitch time            | td_еос_снд               |                                                                                              | -     | 2    | -     | ms   |

| Charge current                         | I <sub>CHG</sub>         | I <sup>2</sup> C programmable in 0.1A steps,<br>0x17 bit[7:2]                                | 0.3   | -    | 3     | А    |

| ICHG current<br>Accuracy 1             | Існд_асс1_снд            | $V_{BAT} = 3.8V, 300 \text{ mA} \le I_{CHG} < 500 \text{ mA}, (T_c = -10^{-70} \text{°C})$   | -20   | _    | 20    | %    |

| ICHG current<br>Accuracy 2             | Існд_асс2_снд            | $V_{BAT} = 3.8V, 500 \text{ mA} \le I_{CHG} < 1,000 \text{ mA}, (T_c = -10^{-70} \text{°C})$ | -10   | _    | 10    | %    |

| ICHG current<br>Accuracy 3             | Існд_ассз_снд            | $V_{BAT} = 3.8V, I_{CHG} \ge 1,000 \text{ mA}$<br>(T <sub>c</sub> = -10~70°C)                | -5    | -    | 5     | %    |

| Pre-charge mode<br>threshold           | Vprechg_chg              | I <sup>2</sup> C programmable in 0.1V steps,<br>V <sub>BAT</sub> rising                      | 2.0   | -    | 3.5   | V    |

| Pre-charge mode<br>hysteresis          | Vprechg_hys_chg          | Pre-charge hysteresis<br>V <sub>BAT</sub> falling                                            | -     | 0.2  | -     | V    |

| Pre-charge threshold accuracy          | Vprechg_acc_chg          |                                                                                              | -5    | -    | 5     | %    |

| Pre-charge current                     | Iprechg_chg              | I <sup>2</sup> C programmable (default)                                                      | -     | 150  | -     | mA   |

| Pre-charge current<br>accuracy         | Iprechg_acc_chg          |                                                                                              | -20   | -    | 20    | %    |

| Trickle charge<br>threshold            | VTRICHG                  | V <sub>BAT</sub> falling                                                                     | -     | 2    | -     | V    |

| Trickle charge<br>threshold hysteresis | VTRICHG_HYS              | V <sub>BAT</sub> rising                                                                      | -     | 200  | -     | mV   |

| Trickle charge<br>threshold accuracy   | VTRICHG_ACC              |                                                                                              | -5    | -    | 5     | %    |

| Trickle current                        | Itrichg                  |                                                                                              | -     | 100  | -     | mA   |

| Trickle current<br>accuracy            | Itrichg_acc              |                                                                                              | -20   | -    | 20    | %    |

| VSYS regulation voltage                | Vsys_min_chg             | I <sup>2</sup> C programmable in 0.1V steps                                                  | 3.3   | -    | 4     | V    |

| VSYS regulation voltage accuracy       | Vsys_min_acc_chg         |                                                                                              | -3    | -    | 3     | %    |

| UUG on-resistance                      | Ron_uug_chg              | From CHG_VIN to CHG_VMID                                                                     | -     | 10   | 30    | mΩ   |

| UG on-resistance                       | Ron_ug_chg               | From CHG_VMID to CHG_VLX                                                                     | -     | 20   | 40    | mΩ   |

| LG on-resistance                       | Ron lg chg               | From CHG_VLX to PGND                                                                         | -     | 20   | 40    | mΩ   |

| PPMOS on-resistance                    | RON_PPMOS_CHG            | From VSYS to VBAT                                                                            | -     | 12   | 30    | mΩ   |

| Switching frequency                    | f <sub>osco_снg</sub>    | I <sup>2</sup> C programmable to 1.5 MHz<br>(default)                                        | -     | 1.5  | -     | MHz  |

| Switching frequency accuracy           | fosc_acc_chg             |                                                                                              | -10   | -    | 10    | %    |

| Maximum duty cycle                     | Dмах_снд                 |                                                                                              | -     | 97   | -     | %    |

| Minimum duty cycle                     | Dміл_сна                 |                                                                                              | 0     | -    | -     | %    |

| VDDP regulation                        | Vvddp_chg                | V <sub>CHG_VIN</sub> = 5.5V                                                                  | 4.5   | 4.9  | 5.3   | V    |

| Charger buck OCP                       |                          | REG0x1D[2] = 1'b0                                                                            | 4     | 6    | 8     |      |

| current                                | ICHG_BUCK_OCP_CHG        | REG0x1D[2] = 1 'b1                                                                           | 5.6   | 8    | 10.4  | A    |

| Internal QONB pull-up resistance       | R <sub>QONB_CHG</sub>    |                                                                                              | 16.15 | 19   | 21.85 | kΩ   |

| Parameter                                              | Symbol                    | Test condition                                               | Min. | Тур. | Max.  | Unit |

|--------------------------------------------------------|---------------------------|--------------------------------------------------------------|------|------|-------|------|

| QONB exit shipping mode duration                       | tshipmode_chg             | CHG_QONB low for BATFET on-<br>time to exit shipping mode    | 0.86 | 0.96 | 1.06  | s    |

| QONB system reset duration                             | t <sub>qonb_rst_chg</sub> | CHG_QONB low time to enable full system reset                | 12   | 15   | 18    | S    |

| BATFET reset time                                      | tbatfet_rst_chg           | BATFET off-time during full system reset                     | 0.6  | 0.66 | 0.72  | S    |

| Shipping mode entry<br>deglitch time                   | td_ship_enter             | Enter shipping mode delay                                    | 15   | 18   | 21.6  | S    |

| AICC threshold                                         | VAICC_VTH                 | V <sub>CHG_VIN</sub> rising<br>I <sup>2</sup> C programmable | -    | 4.6  | -     | V    |

| AICC hysteresis                                        | VAICC_HYS_VTH             |                                                              | -    | 50   | -     | mV   |

| OTG output regulation                                  | VBSTCV_CHG                | I <sup>2</sup> C programmable default                        | -    | 5.05 | -     | V    |

| OTG output accuracy                                    | VBSTCV_ACC_CHG            | I <sub>LOAD</sub> = 0 mA                                     | -3   | -    | 3     | %    |

| OTG over-load<br>protection threshold                  | I <sub>BST_0.5A_CHG</sub> | OTG_OC = 0.5A<br>REG 0x1A[2:0] = 000                         | 0.5  | -    | -     | А    |

| OTG CHG_VMID over-<br>voltage protection<br>threshold  | VMIDOVP_OTG_CHG           | VCHG_VMID rising                                             | 5.72 | 6    | 6.28  | V    |

| OTG CHG_VMID over-<br>voltage protection<br>hysteresis | VMIDOVP_OTG_HYS_CHG       |                                                              | -    | 200  | -     | mV   |

| OTG VBAT under-<br>voltage protection<br>threshold     | VBAT_UVP_OTG_CHG          | $I^2C$ default, $V_{BAT}$ falling                            | 2.62 | 2.8  | 2.98  | V    |

| OTG VBAT under-<br>voltage protection<br>hysteresis    | VBAT_UVP_OTG_HYS_CHG      | V <sub>BAT</sub> rising                                      | -    | 400  | -     | mV   |

| Boost supply current                                   | BOOST_SUPPLY              | OTG mode, ILOAD = 0 mA                                       | -    | 8    | -     | mA   |

| OTG over-current<br>protection threshold               | Іотд_оср_снд              | Default = 6.5A                                               | 5.2  | 6.5  | 8.2   | А    |

| Pull-down ability on CHG_ENB                           | IPD_CHG_ENB               |                                                              | -    | 1    | 2.3   | μΑ   |

| D+/D- detection                                        |                           | · · · · · · · · · · · · · · · · · · ·                        |      |      |       |      |

| D+ source voltage                                      | Vdp_src                   |                                                              | 0.5  | 0.6  | 0.7   | V    |

| Data detect voltage                                    | V <sub>DAT_REF</sub>      |                                                              | 0.25 | 0.3  | 0.4   | V    |

| VLGC voltage                                           | VLGC_CHG                  |                                                              | 0.8  | -    | 2     | V    |

| D- sink current                                        | Idm_sink                  |                                                              | 50   | 100  | 150   | μΑ   |

| Data contract detect<br>current source                 | Idp_src                   |                                                              | 7    | -    | 13    | μΑ   |

| Dedicated charging<br>port resistance across<br>D+/-   | R <sub>D+D-DCP</sub>      | sEN_DCP = 1                                                  | 50   | 90   | 130   | Ω    |

| D+ source on-time                                      | t <sub>DP_SRC_ON</sub>    |                                                              | 40   | 64   | -     | ms   |

| DCD timeout                                            | t <sub>DCD_TIMEOUT</sub>  |                                                              | 300  | -    | 1,200 | ms   |

| D+ source off to high<br>current                       | tdpsrc_hicrnt             |                                                              | 28   | 32   | 36    | ms   |

| Charger detect<br>debounce                             | tchgr_det_dbnc            |                                                              | 27   | 30   | 33    | ms   |

| CHRDETB                                                |                           |                                                              |      |      |       |      |

| Parameter              | Symbol                      | Test condition                                         | Min. | Тур.     | Max.   | Unit |

|------------------------|-----------------------------|--------------------------------------------------------|------|----------|--------|------|

| PD_VBUS over-voltage   |                             |                                                        |      |          |        |      |

| protection threshold   | VPD_VBUS_OVP                | V <sub>PD_VUS_OVP</sub> rising, I <sup>2</sup> C       | 6    | -        | 14.5   | V    |

| range                  |                             | programmable (default 10.5V)                           | -    |          | _      |      |

| PD_VBUS over-voltage   |                             |                                                        |      |          |        |      |

| protection accuracy    | VPD_VBUS_OVP_ACC            |                                                        | -3   | -        | 3      | %    |

| PD_VBUS over-voltage   |                             |                                                        |      |          |        |      |

| protection hysteresis  | VPD_VBUS_HYS                |                                                        | -    | 150      | -      | mV   |

| PD_VBUS_UVLO           |                             | VPD_VUS_UVLO falling, I <sup>2</sup> C                 |      |          |        |      |

| protection threshold   | VPD_VBUS_UVLO               | programmable 0.1V/Step (default                        | 2.6  | -        | 3.7    | V    |

| •                      | V PD_VBUS_UVLO              | 3.7V)                                                  | 2.0  | _        | 5.7    | v    |

| range                  |                             | 3.7 V)                                                 |      |          |        |      |

| PD_VBUS UVLO           | VPD_VBUS_UVLO_ACC           |                                                        | -4   | -        | 4      | %    |

| protection accuracy    |                             |                                                        |      |          |        |      |

| PD_VBUS UVLO           | VPD_VBUS_UVLO_HYS_          |                                                        | -    | 150      | -      | mV   |

| protection hysteresis  |                             |                                                        |      |          |        |      |

| ADC                    | T                           |                                                        |      |          |        |      |

|                        |                             | Only for one channel, 0x56[5:3] = 0                    |      |          |        |      |

| ADC conversion time    | tconv_adc                   | ms of waiting time and 0x58[7:0] =                     | 20.8 | 26       | 31.2   | ms   |

|                        |                             | 0 ms of idle time                                      |      |          |        |      |

| Number of bits for ADC | D                           |                                                        |      | 12       | _      | bit  |

| resolution             | Res_adc                     |                                                        | -    | 12       | -      | DIL  |

| CHG_VIN_DIV5           |                             |                                                        | 4    |          | 22     | .,   |

| measurement range      | Vvbus_div5_adc_range        |                                                        | 1    | -        | 22     | V    |

| CHG_VIN_DIV5           |                             |                                                        |      |          |        |      |

| resolution             | Vvbus_div5adc_res           |                                                        | -    | 25       | -      | mV   |

| CHG_VIN_DIV5           |                             |                                                        |      |          |        |      |

| accuracy               | Vvbus_div5adc_acc           |                                                        | -3   | -        | 3      | LSB  |

| CHG_VIN_DIV2           |                             |                                                        |      |          |        |      |

| measurement range      | $V_{VBUS_DIV2\_ADC\_RANGE}$ |                                                        | 1    | -        | VDDA*2 | V    |

| CHG_VIN_DIV2           |                             |                                                        |      |          |        |      |

| resolution             | Vvbus_div2adc_res           |                                                        | -    | 10       | -      | mV   |

|                        |                             |                                                        |      |          |        |      |

| CHG_VIN_DIV2           | VVBUS_DIV2ADC_ACC           |                                                        | -3   | -        | 3      | LSB  |

| accuracy               |                             |                                                        |      |          |        |      |

| VBAT measurement       | VBAT_ADC_RANGE              |                                                        | 0    | -        | VDDA   | V    |

| range                  |                             |                                                        | -    |          |        |      |

| VBAT resolution        | VBAT_ADC_RES                |                                                        | -    | 5        | -      | mV   |

| VBAT accuracy          | V <sub>BAT_ADC_ACC</sub>    |                                                        | -3   | -        | 3      | LSB  |

| VSYS measurement       | M                           |                                                        | 0    |          |        | V    |

| range                  | Vsys_adc_range              |                                                        | 0    | -        | VDDA   | V    |

| VSYS resolution        | V <sub>SYS_ADC_RES</sub>    |                                                        | -    | 5        | -      | mV   |

| VSYS accuracy          | Vsys_adc_acc                |                                                        | -3   | -        | 3      | LSB  |

| IBUS measurement       |                             |                                                        | -    |          | -      |      |

| range                  | IBUS_ADC_RANGE              |                                                        | 0    | -        | 5      | А    |

| IBUS resolution        | libus adc res               | + +                                                    | _    | 50       | _      | mA   |

|                        | IBUS_ADC_KES                |                                                        | -    | 50       |        | 11A  |

|                        |                             | $I_{BUS} > 2A$ , IAICR [7:2] setting $\geq 400$ mA     | -3   | -        | 3      |      |

| IBUS accuracy          | libus adc acc               | $I_{BUS} < 2A$ , IAICR [7:2] setting $\geq 400$        | -2   | -        | 2      | LSB  |

| 1                      |                             | mA                                                     |      | <u> </u> |        |      |

|                        |                             | I <sub>BUS</sub> < 2A, IAICR [7:2] setting < 400<br>mA | -2   | -        | 2      |      |

|                        | 1                           |                                                        |      |          | 1      |      |

| IBAT measurement       |                             |                                                        |      |          | 5      |      |

| Parameter                            | Symbol                       | Test condition                                       | Min.  | Тур.  | Max.          | Unit |

|--------------------------------------|------------------------------|------------------------------------------------------|-------|-------|---------------|------|

| IBAT resolution                      | libat_adc_res                |                                                      | -     | 50    | -             | mA   |

| IBAT accuracy                        | IIBAT_ADC_ACC                |                                                      | -2    | -     | 2             | LSB  |

| TEMP_JC measurement<br>range         | Ttemp_jc_adc_range           |                                                      | -40   | -     | 120           | °C   |

| TEMP_JC resolution                   | TTEMP JC ADC RES             |                                                      | -     | 2     | -             | °C   |

| TEMP_JC accuracy                     | T <sub>TEMP_JC_ADC_ACC</sub> | Temperature < 85°C                                   | -3    | -     | 3             | LSB  |

| VREF_TS pull-up<br>voltage           | V <sub>REF_TS_ADC</sub>      |                                                      | 1.782 | 1.8   | 1.818         | V    |

| TS voltage<br>measurement range      | VTS_ADC_RANGE                |                                                      | 0     | -     | VDDA          | V    |

| TS resolution                        | VTS_ADC_RES                  |                                                      | -     | 5     | -             | mV   |